XRF螢光光譜分析/鑫知識文章二十五、淺談半導體先進製程 奈米製程是什麼

次閱讀

在現今電子製造的產業中,有能力將半導體製程推進到7nm以下的業者,僅剩下三星電子、台積電和英特爾。因此在先進製程的對抗,也就是這三家業者之間的競爭,甚至可以說,誰能勝出,誰就有希望取得絕對的市場優勢。

文章二十五、淺談半導體先進製程 奈米製程是什麼

在現今電子製造的產業中,有能力將半導體製程推進到7nm以下的業者,僅剩下三星電子、台積電和英特爾。因此在先進製程的對抗,也就是這三家業者之間的競爭,甚至可以說,誰能勝出,誰就有希望取得絕對的市場優勢。

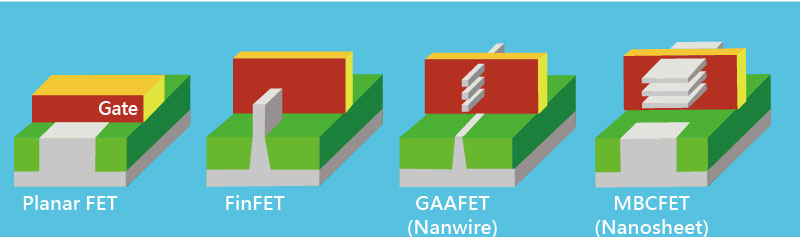

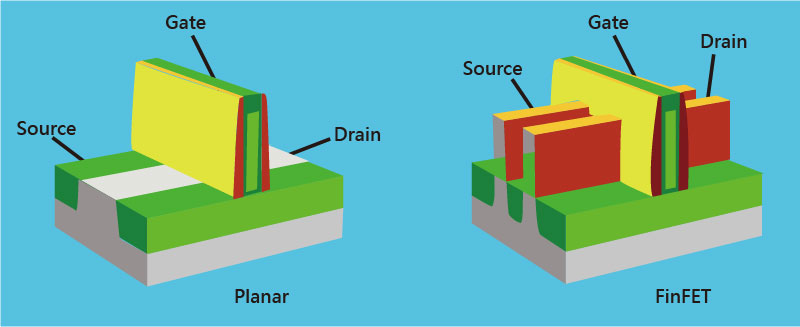

業界25nm以上,多數為(PlanarFET)平面結構方式。

目前三星和台積電的7nm和5nm製程,都是使用鰭式電晶體(FinFET)的立體架構。該製程的問世就是因為平面的微縮技術在25nm以下遇到瓶頸,為了持續推進摩爾定律,同時改進電力損耗的問題,因此轉採用這種立體的架構。

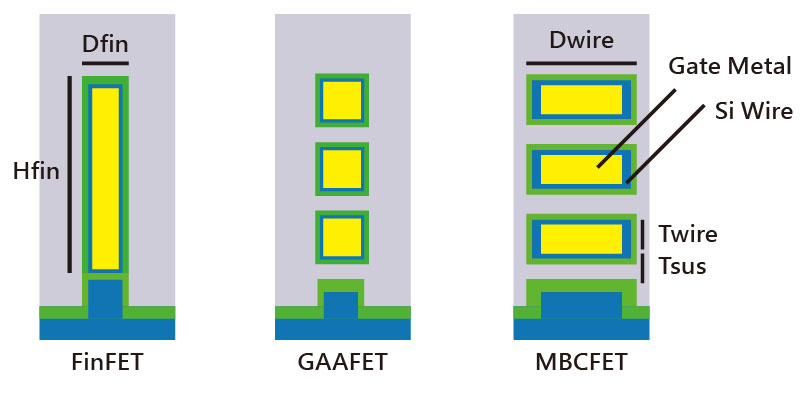

首先,須要先理解何謂GAA製程。顧名思義,GAA就是整面都是閘極的意思,而這是相對於FinFET來說,因為在FinFET的架構中,金屬閘極只包覆了三面,而GAA則是全面性的包覆,一種環狀的結構。

而有別於側邊鰭片式的結構,Nanowire FET改以奈米線來取代,藉以增加更多的半導體電路,然後再以閘極來包覆奈米線,以提高對於電路的控制和穩定性;而不同於Nanowire FET(GAAFET),Nanosheet FET(MBCFET)是使用更寬更薄的「sheet」來取代,但同樣也使用閘極來包覆。這兩者各有優勢,但從量產的設備相容性以及難度來說,Nanosheet FET(MBCFET)似乎多了些青睞。

然而製程發展到3nm將會是一個重要的技術分界點為什麼3nm製程如此關鍵,最主要的原因就是當前的微縮製程走到3nm,將會面臨新的物理極限,除非改用新的結構,否則摩爾定律就很難再維持下去。這項突破也就是GAAFET(Gate-All-Around,GAA)

FinFET即將退場 3nm帶起新製程大戰

但使用突出鰭式設計的FinFET架構,到了3nm之後也將面臨微縮的問題,過細的鰭片也將會遭遇電流控制的問題,同時也會失去對某些電場效應的抗性(例如靜電),因此提出新架構就成了3nm製程的兵家之地。

以三星電子為例,日前公布的3nm技術內容裡就特別指出,將使用一種閘極全環(Gate-All-Around,GAA)製程為基礎的MBCFET架構。而MBCFET則是多橋通道場效電晶體(Multi-Bridge Channel Field-Effect Transistor),並透過所謂的GAA製程來包覆。從三星的技術說明會裡,它應該是一種Nanosheet FET(MBCFET)架構的技術。

使用新製程所生產的3nm晶片的效能也相當卓越,從三星電子公布的測試資料顯示,相較於7nm製程,使用其MBCFET的3nm產品效能提升了35%,功耗則大幅下降了50%,同時面積也縮減了45%。其躍進的幅度可說是十分驚人。而反觀台積電,儘管沒有針對3nm技術有太多的說明,但台積電對於其製程微縮的能力依然非常有自信,不僅表示3nm的研發正如期進行中,而且1nm的門檻目前看來也有望跨越。

就現階段來看,台積電則是全力推進5nm的製程量產化,且其目前使用的5nm製程為FinFET已有成熟且穩定的製程技術,其中能強壓三星的關鍵在於,台積電擁有超高的生產良率,其製程耗損量減少,也就是高獲利的保證。然而,雖然看似目前台積電坐穩寶座,三星緊追在後,但可別忘了三國鼎立的另一位強權-英特爾(Intel),據外媒報導,台積電與三星電子至少都已進入3nm,不過台積電與三星電子只是名義上的製程,實際的電晶體規模密度卻是落後Intel一個世代,因此在未來的半導體奈米製程領域,三強鼎立角逐王位,誰能笑著站到最後還很難說。

半導體製造業三巨頭角逐3奈米製程技術,未來誰能一家獨大尚未揭曉。

知識文章出處:https://www.wpgdadatong.com/tw/blog/detail?BID=B1562

圖片出處:維基百科